RiscV

- • 100%www.tomshardware.com RISC-V CPU demoed with RX 7900 XTX GPU in Debian Linux — AMD flagship GPU paired with Milk-V Megrez board and SiFive P550 cores

The 7900 XTX was able to run the glmark2 benchmark.

Crossposted from https://lemmy.ml/post/21673583 ----- RISC-V International, the global standards organization, today announced that the RVA23 Profile is now ratified. RVA Profiles align implementations of RISC-V 64-bit application processors that will run rich operating systems (OS) stacks from standard binary OS distributions. RVA Profiles are essential to software portability across many hardware implementations and help to avoid vendor lock-in. The newly ratified RVA23 Profile is a major release for the RISC-V software ecosystem and will help accelerate widespread implementation among toolchains and operating systems.

Each Profile specifies which ISA features are mandatory or optional, providing a common target for software developers. Mandatory extensions can be assumed to be present, and optional extensions can be discovered at runtime and leveraged by optimized middleware, libraries, and applications.

Key Components of RVA23 Include:

- Vector Extension: The Vector extension accelerates math-intensive workloads, including AI/ML, cryptography, and compression / decompression. Vector extensions yield better performance in mobile and computing applications with RVA23 as the baseline requirement for the Android RISC-V ABI.

- Hypervisor Extension: The Hypervisor extension will enable virtualization for enterprise workloads in both on-premises server and cloud computing applications. This will accelerate the development of RISC-V-based enterprise hardware, operating systems, and software workloads. The Hypervisor extension will also provide better security for mobile applications by separating secure and non-secure components.

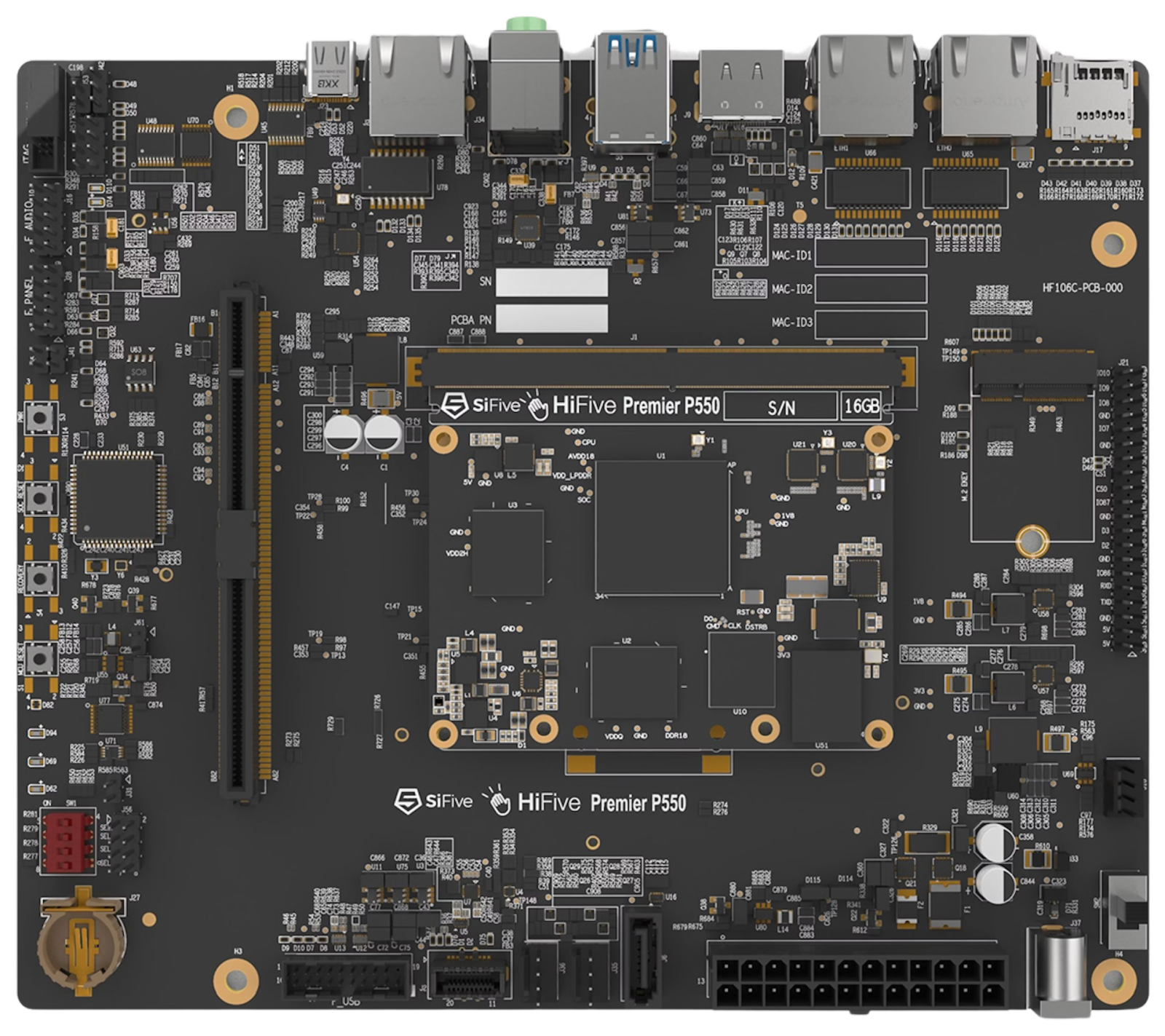

- • 100%liliputing.com SiFive HiFive Premiere P550 RISC-V board is now available for developers (in very limited quantities) - Liliputing

SiFive HiFive Premiere P550 RISC-V board is now available for developers (in very limited quantities)

- • 100%liliputing.com Yuzuki Avaota-A1 is a $55 single-board PC with 8 ARM Cortex-A55 CPU cores and an embedded RISC-V core - Liliputing

Yuzuki Avaota-A1 is a $55 single-board PC with 8 ARM Cortex-A55 CPU cores and an embedded RISC-V core

- • 100%www.sifive.com Samsung Highlights Work to Bring RISC-V to Tizen

Samsung using SiFive P470 to bring RISC-V to TIzen

cross-posted from: https://lemmy.world/post/20499594

- • 100%www.pragmaticsemi.com A Bendable Non-silicon RISC-V Microprocessor - Pragmatic Semiconductor

Today Nature journal publishes Pragmatic Semiconductor’s latest research article, a Bendable Non-silicon RISC-V Microprocessor, demonstrating the world’s first 32-bit microprocessor in a flexible technology that is fully functional while flexed. It’s also the first flexible microprocessor with embed...

cross-posted from: https://lemmy.world/post/20236242

- www.cnx-software.com ESP32-C6 WiFi 6 and Bluetooth 5.0 USB-C development board integrates 1.47-inch TFT LCD Display - CNX Software

Waveshare's ESP32-C6-LCD-1.47 board features a 1.47-inch display, WiFi 6 and Bluetooth 5 connectivity for IoT and HMI projects.

- www.cnx-software.com Using RISC-V cores on the Raspberry Pi Pico 2 board and RP2350 MCU - From blinking an LED to building Linux - CNX Software

Raspberry Pi Pico 2 was released last month with a Raspberry Pi RP2350 microcontroller equipped with two Arm Cortex-M33 cores and two 32-bit RISC-V

- www.theregister.com Tenstorrent details its RISC-V packed Blackhole chips

Shove 32 of 'em in a box and you've got nearly 24 petaFLOPS of FP8 perf

cross-posted from: https://lemm.ee/post/36499892

> cross-posted from: https://lemm.ee/post/36499694 > > > Hope everyone is having a relaxing Sunday morning/evening. > > > > I wanted to follow up from my previous post, as some of you have indicated interest. > > > > About logistic considerations, I believe 8 weeks is a good time commitment for a hardware project. The goal is to learn more about silicon manufacturing, lower-level computer hardware details such as architecture, circuit design, fundamental condensed matter physics, and digital logic design. Other goals involve understanding firmware systems such as BIOS and the cascade of events that occur from power-on to user operation as well as conceptualizing the small timescales that these events occur on. My intention is not to dictate the philosophy of learning, but bring awareness to details that otherwise would have never been known or to draw a larger picture using the constellation of components that is a modern computing device. We then will delve into HDLs (Hardware description languages) and look specifically at the VHDL (Verilog HDL) for how to design a chip. This is where my understanding of what is out there becomes fuzzy. > > > > We will need a repository to store documents. It is not my intention to use Google Drive. Is there a trusted platform that offers this functionality? I am also curious as to learning a VCS (Version Control System). Git seems to be the choice for this. Maintaining our codebase, resources/references, questions/comments, presentations, notes, and miscellaneous documents in some platform that does not infringe on user privacy. Any ideas in this domain? > > > > Individual development environments are also crucial to a productive hobby/working session. I think it'd be fun to discuss IDEs, TUI environments, barebones software to accomplish simple tasks, CLI navigation, file system implementation, and drive partitioning. Some of you are adept TUI text editor users, which your expertise would be greatly appreciated. > > > > Because this is Lemmy, I assume most of us are interested in FOSS software/hardware. Perhaps there are open source architectures for GPUs, RAM devices, and other fundamental computing units. > > > > Is there a such thing as open source RAM architectures? Is that even the correct question to pose? I see that "OpenRAM" exists for ASIC design. Maybe we can have an ultra-specific computing task that we could optimize all the constituent hardware pieces to perform. Maybe a game engine for a programming project, but where we patchwork the pieces, or at least examine the guts of Godot together. I've found that discussing how one actually READS documentation, can be helpful in becoming more independent during information searching. > > > > Apologies if some parts are still unclear. I'm just happy to see some of you are interested! As per the survey and what you'd like to get out of something like this, or if the idea needs other parts glued together, feel free to suggest them here. Looking forward to your feedback.

- • 93%frame.work Introducing a new RISC-V Mainboard from DeepComputing

We’re excited to share a preview of a Framework Laptop 13 Mainboard with a new CPU architecture.

cross-posted from: https://feddit.cl/post/3171211

- https:// canonical.com /blog/worlds-first-risc-v-laptop-gets-a-massive-upgrade-and-equips-with-ubuntu

cross-posted from: https://feddit.cl/post/3120695

My unfunded speculation is that this will quite expensive and a bit hard to boot other thing different that Ubuntu.

Title. Just curious since apparently risc-v is mentioned as a "ultra low power draw" CPU... so I'd like to know if that is true. Thanks in advance.

- https:// semiengineering.com /risc-v-wants-all-your-cores/

RISC-V intl. announces plans to add matrix multiplication to the ISA, in an attempt to turn the architecture into a general-purpose solution for all processor derivatives eg. GPUs, TPUs, DSPs, Security Processors, Power management processors.

This isn't a rip on RISC-V but it's something I notice a lot with ARM and RISC SBCs compared to x86, which seems to support Linux, Windows, MacOS regardless of the device specs.

On other platforms, the developers have to build special iso images for each device, even though the underlying OS supports the whole architecture.

If I wanted to move to a new device (say, upgrade my Raspberry pi 4B to an Orange Pi, or other RISC-V alternatives) I'd have to ensure the new device had support from my OS choice, download a new image for it, and manually port stuff across. (as far as I can tell).

What's the technical reason that x86 can configure the OS on the fly but ARM/RISC can't?

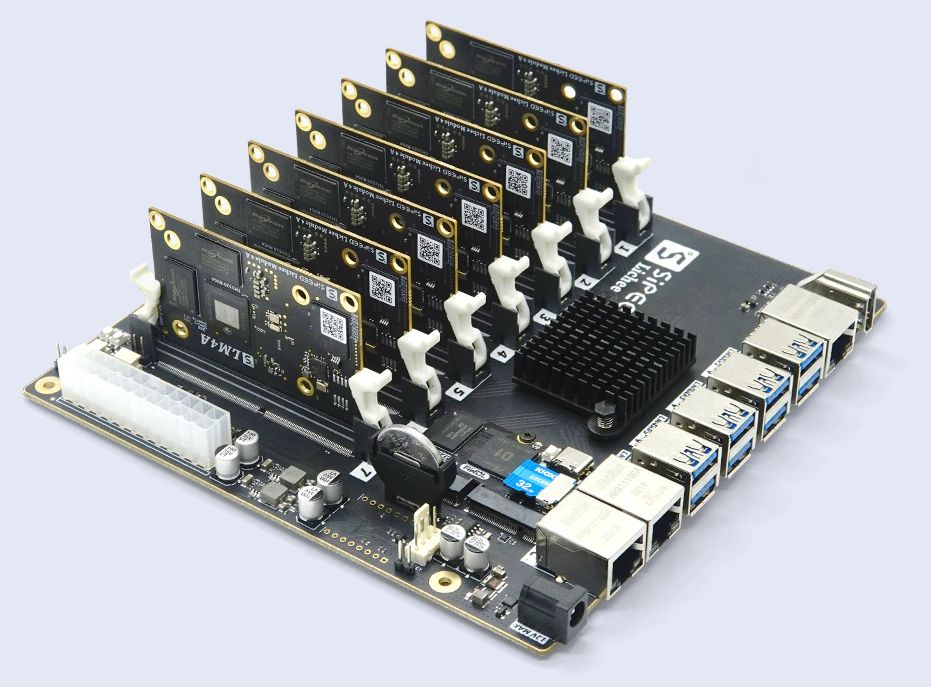

- liliputing.com Sipeed Lichee Cluster 4A board now available (supports up to 7 RISC-V computer modules) - Liliputing

Sipeed Lichee Cluster 4A board now available (supports up to 7 RISC-V computer modules)

- https:// agra.informatik.uni-bremen.de /doc/konf/TFP23_ST.pdf

Abstract. Formal languages are commonly used to model the seman- tics of instruction set architectures (e.g. ARM). The majority of prior work on these formal languages focuses on concrete instruction execu- tion and validation tasks. We present a novel Haskell-based modelling approach which allows the creation of flexible and versatile architecture models based on free monads and a custom expression language. Con- trary to existing work, our approach does not make any assumptions regarding the representation of memory and register values. This way, we can implement non-concrete software analysis techniques (e.g. sym- bolic execution where values are SMT expressions) on top of our model as interpreters for this model. In contrast to prior work, our modelling approach is therefore explicitly focused on the creation of custom ISA in- terpreters. We employ our outlined approach to create an abstract model and a concrete interpreter for the RISC-V base instruction set. Based on this model, we demonstrate that custom interpreters can be implemented with minimal effort using dynamic information flow tracking as a case study.

- www.sohu.com The State of RISC-V Instruction Set Architecture in China_the_and_Visual

Regarding the progress of the “domestic open-source RISC-V”-- "Xiangshan" project, Bao revealed to Ti…

This seems to be a good summary of the recent RISC-V conference in China.

Top quotes from the article :

Data shows that by 2022, the cumulative shipment of RISC-V chips worldwide reached 10 billion.

According to Counterpoint Research's prediction, by 2025, the cumulative shipment of RISC-V processors will exceed 80 billion units, with a compound annual growth rate (CAGR) of 114.9%. By then, RISC-V will account for 14% of the global CPU market, 28% of the IoT market, 12% of the industrial market, and 10% of the automotive market.

According to research firm Semico, the number of RISC-V chips is expected to grow by a CAGR of 73.6% from 2023 to 2027, producing approximately 25 billion AI chips based on the RISC-V, with revenues reaching $291 billion.

Beijing Open Source Chip (BOSC) announced the second generation "XiangShan", an open-source high-performance RISC-V processor core, which has surpassed ARM A76 in performance... "Nanhu" architecture has completed "productization transformation"... In 2022, two companies have applied "Xiangshan-Nanhu". One of them has taped out the chips and will receive samples in September this year, and another will tape out in the second half of this year.

The third-generation "Kunminghu" architecture is under development, and its performance can be comparable to ARM Neoverse N2. Xiangshan-Kunminghu has a chance to reach the level of high-performance processor cores of ARM two or three years ago, but it is only in terms of performance. Its area and power consumption, where ARM has a strong advantage, still need to be optimized.

YouTube Video

Click to view this content.

> Sipeed Lichee Pi 4A RISC-V SBC review and Debian demo. This is the first RISC-V computer I’ve tested that's provided a usable desktop computing experience right out of the box. End-user RISC-V is starting to arrive! :) > > You can learn more about the Lichee Pi 4A on its web page here: > https://sipeed.com/licheepi4a > > And the board has excellent documentation here: > https://wiki.sipeed.com/licheepi4a.html > > Note that the hardware I used in this video was purchased from AliExpress: > https://www.aliexpress.com/item/10050... > > I have reviewed four previous RISC-V SBCs, including the StarFive VisionFive 2, which also (after some messing around) provides a good desktop experience: > > > • VisionFive 2: RISC-V Quad Core Low Co... > > I also have an 2023 update on RISC-V developments here: > > > • RISC-V 2023 Update: From Embedded Com... > > And my general introduction to RISC-V is here: > > > • Explaining RISC-V: An x86 & ARM Alter... > > For additional ExplainingComputers videos and other content, you learn about becoming a channel member here: > > > / @explainingcomputers > > More videos on computing and related topics can be found at: > > > / @explainingcomputers > > You may also like my ExplainingTheFuture channel at: > > / @explainingthefuture > > Chapters: > 00:00 Introduction > 00:45 Unboxing > 03:33 Specifications > 07:26 First Boot > 10:37 Debian Demo > 18:10 Another Milestone

- • 100%thenextweb.com How RISC-V can usurp Arm as the Switzerland of computer chips

Arm's status as the Switzerland of computer chips faces a growing threat from an open-source rival: RISC-V.

- www.businesswire.com OpenHW Group Announces Tape Out of RISC-V-based CORE-V MCU Development Kit for IoT Built with Open-Source Hardware & Software

OpenHW Group today announced that the industry’s most comprehensive Development Kit for an open-source RISC-V MCU is now available to be ordered. The

- wccftech.com Jim Keller's Tenstorrent Wants To Compete With NVIDIA's AI GPUs Using RISC-V Based AI CPUs

Tenstorrent's CEO, Jim Keller, revealed an updated RISC-V product roadmap & how he plans to tackle NVIDIA AI dominance using CPUs & not GPUs.

Somebody made a list of RiscV SBCs

- www.eetimes.com Jim Keller on AI, RISC-V, Tenstorrent’s Move to Edge IP - EE Times

The legendary CPU architect Jim Keller discusses Tenstorrent’s strategy, RISC-V and the future of AI in an exclusive interview with EE Times.

“My belief is in the next 5 to 10 years, RISC-V will take over all the data centers,” Keller told EE Times